2025年2月14日,77779193永利集团彭海琳教授研究团队与永利集团电子学院邱晨光研究员团队在《自然—材料》(Nature Materials)在线发表题为“Low-power 2D gate-all-around logics via epitaxial monolithic 3D integration”的研究论文,报道了世界首例低功耗二维环栅晶体管(2D GAAFET),并研制出高性能低功耗二维环栅逻辑器件。

二维环栅晶体管技术是后摩尔时代突破硅基晶体管物理极限的重要路径之一,其关键在于结合二维半导体的高迁移率与环栅(Gate-All-Around, GAA)结构的强栅控能力,以实现更高性能、更低功耗的器件,但面临的挑战是二维沟道与环栅介质的原子级均匀尺寸控制和界面结构精确控制。该工作制备的高迁移率二维半导体纳米片沟道Bi2O2Se由外延型单晶高κ原生氧化物栅β-Bi2SeO5完全包围,形成高质量全环栅异质结构(2DBi2O2Se/Bi2SeO5 GAA),具有原子级平整界面和超薄的沟道厚度(达1个单胞厚度,~1.2纳米)以及超薄的栅介质厚度(等效氧化层厚度EOT可低至0.28纳米),还可实现晶圆级单片三维集成(M3D)。

基于外延集成型Bi2O2Se/Bi2SeO5环栅异质结的二维环栅晶体管(2D GAAFET)具有原子级均匀的沟道与栅氧化层厚度,低的界面缺陷密度,高的电子迁移率,高的电流开关比,近热力学极限的亚阈值摆幅,更好的沟道控制和静电性能。该晶体管的性能与能效同时超过了传统硅基晶体管的物理极限,是世界上迄今速度最快、能耗最低的晶体管。该原创性工作突破了后摩尔时代高速低功耗芯片的二维新材料精准合成与新架构三维异质集成瓶颈,为开发未来先进芯片技术带来新机遇。

集成电路是信息时代重要的技术基础,也是国家战略竞争力的重要标志。先进制程集成电路制造作为半导体工业技术的“明珠”,对带动人工智能(AI)、云计算、大数据、5G通信等新兴信息技术发展和产业增长发挥着关键作用,对以实现数据的高速处理和传输、信息安全等功能为基础的国家信息化、数字化发展提供关键支撑。先进制程集成电路制造已成为全球半导体产业的“兵家必争之地”,推动了科技领域的快速发展。

功耗约束下的器件尺寸微缩和集成密度提升始终是先进制程集成电路技术发展和演进的核心。随着大规模集成电路(VLSI)技术的持续发展,来自短沟效应、量子隧穿以及寄生效应等问题的挑战,使得以传统硅基半导体/氧化物(如Si/SiO2、Si/HfO2)为核心的CMOS(互补金属氧化物半导体)器件技术难以通过尺寸的持续微缩维持芯片迭代的需求。能耗上升和算力不足等问题成为延续摩尔定律的最大瓶颈。探索“后摩尔时代”器件新原理、新材料、新工艺和新架构,实现更高密度、更低功耗、更高算力的芯片设计与制造,成为推动传统集成电路芯片变革的关键。

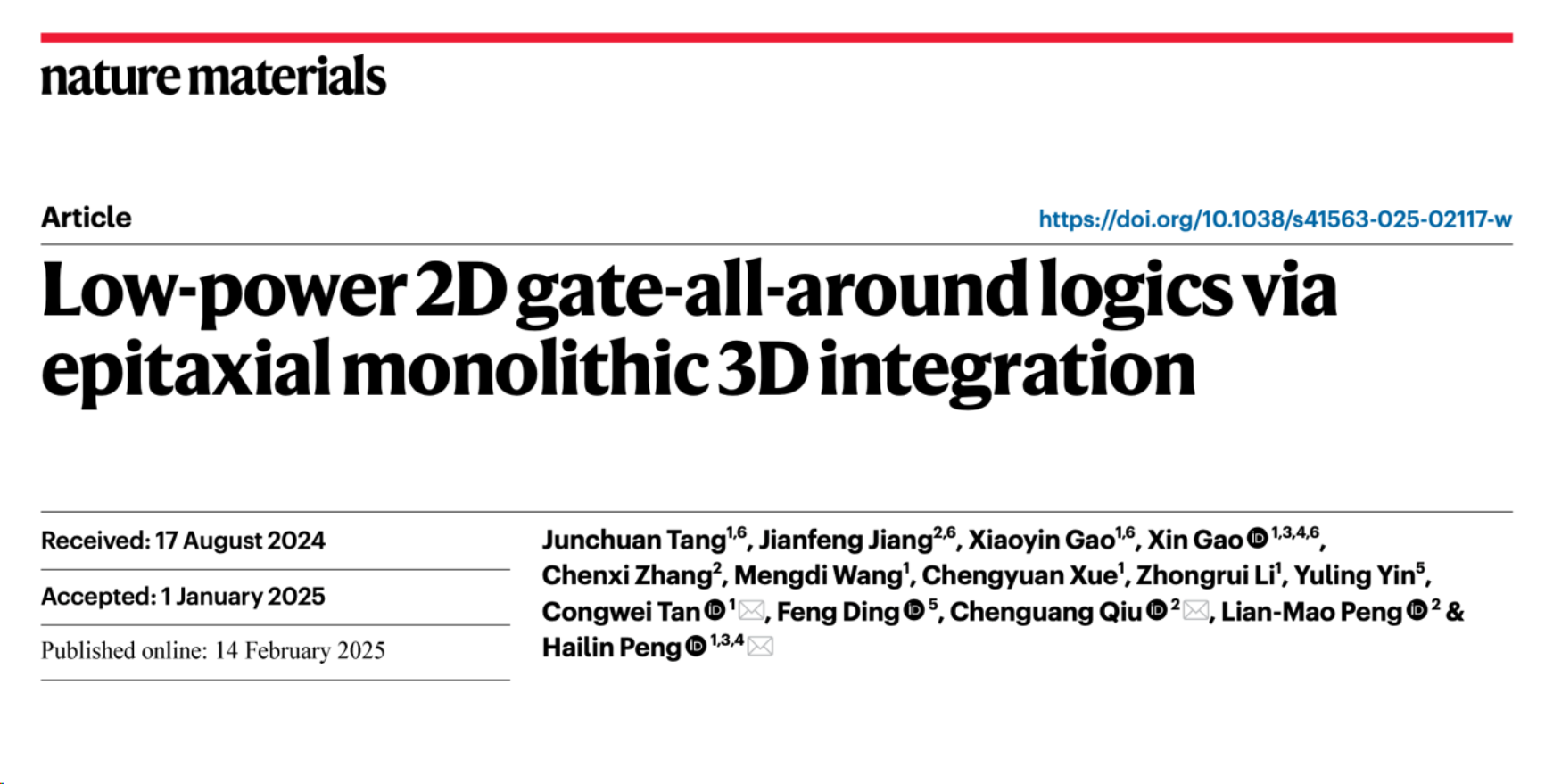

图1. 二维环栅晶体管及三维异质集成示意图。

材料与架构的创新催生了集成电路在性能、密度和功耗方面的新突破。集成电路技术发展的近30年里,硅基CMOS器件在“摩尔定律”的驱使下不断微缩,器件架构逐渐从平面器件发展到鳍式场效应晶体管(FinFET)器件以增强栅极对通道的控制能力。依靠新材料和新结构的发展,FinFET器件技术融合铜金属互联技术、应力硅技术、高κ金属栅(HKMG,High-κMetal Gate)工艺技术,助力摩尔定律持续向前发展,从22纳米技术节点发展到当前的3纳米技术节点。但是,在3纳米节点以下,传统硅基FinFET的栅极对沟道的控制能力减弱,导致漏电流增加和功耗上升,FinFET技术发展将面临物理极限与工艺难度挑战,无法持续微缩。应对这一挑战,一种硅基纳米片沟道被栅极四面全环绕包围的环栅晶体管(GAAFET)新架构器件技术应运而生。GAAFET将显著抑制短沟道效应,进一步增强栅极对沟道电流的控制,降低漏电,具有更高的速度和更低的功耗。随着先进工艺节点持续推进,国际半导体产业界已明确2纳米以后晶体管技术将由当前的鳍式晶体管(FinFET)转向更先进的纳米片环栅晶体管(GAAFET)制程技术。

技术节点进入埃米世代,二维(2D)半导体因其具有表面无悬挂键、原子级均匀厚度和高迁移率等特性,可突破传统硅基晶体管本征物理极限(极限栅长将停止在12 nm,工作电压不能小于0.6 V),实现更短的栅长、出色的栅控、高驱动电流、单片三维(M3D)集成,可作为“后硅材料”延续CMOS器件微缩,提高芯片集成度、算力和能效。为此,全球众多知名半导体公司和研究机构,如英特尔(Intel)、台积电(TSMC)、以及欧洲微电子中心(IMEC)等,都在致力于二维环栅晶体管(2D GAAFET)的研发。然而,2D GAAFET的器件制造面临源漏接触、栅介质材料及界面等多重挑战,性能仍无法与业界硅基晶体管相媲美。低功耗、高性能的2D GAAFET器件制造更是需要解决二维沟道/全环绕超薄栅介质的原子级尺寸控制和界面结构精确调控的世界难题。新型高迁移率二维半导体沟道和高κ氧化物环栅异质结的精准制备及三维异质集成等关键科学问题(图1),已成为各国半导体技术竞争的国际焦点。

图2. 二维Bi2O2Se/Bi2SeO5环栅外延异质结与三维异质集成。(a-c)晶圆级多叠层二维铋基环栅异质结的示意图(a)、截面透射表征与元素分析(b)和光学照片(c);二维铋基环栅晶体管的原子级平整界面(d, e)。

近年来,永利集团彭海琳课题组开发了一种新型超高迁移率二维铋基半导体(硒氧化铋Bi2O2Se)及其高κ原生氧化物栅介质材料(α-Bi2SeO5与β-Bi2SeO5),并基于此体系制备了一系列高性能二维晶体管、红外探测器、传感器以及量子霍尔器件(Nature Nanotech. 2017, 12, 530; Nature Commun. 2018, 9, 3311; Nature Electron. 2020, 3, 473; Nature Electron. 2022, 5, 643; Nature Mater. 2023, 22, 832; Nature Nanotech. 2024, 19, 1452),并率先开发出世界上首例外延高κ栅介质集成型二维鳍式晶体管(Nature 2023, 616, 66)。

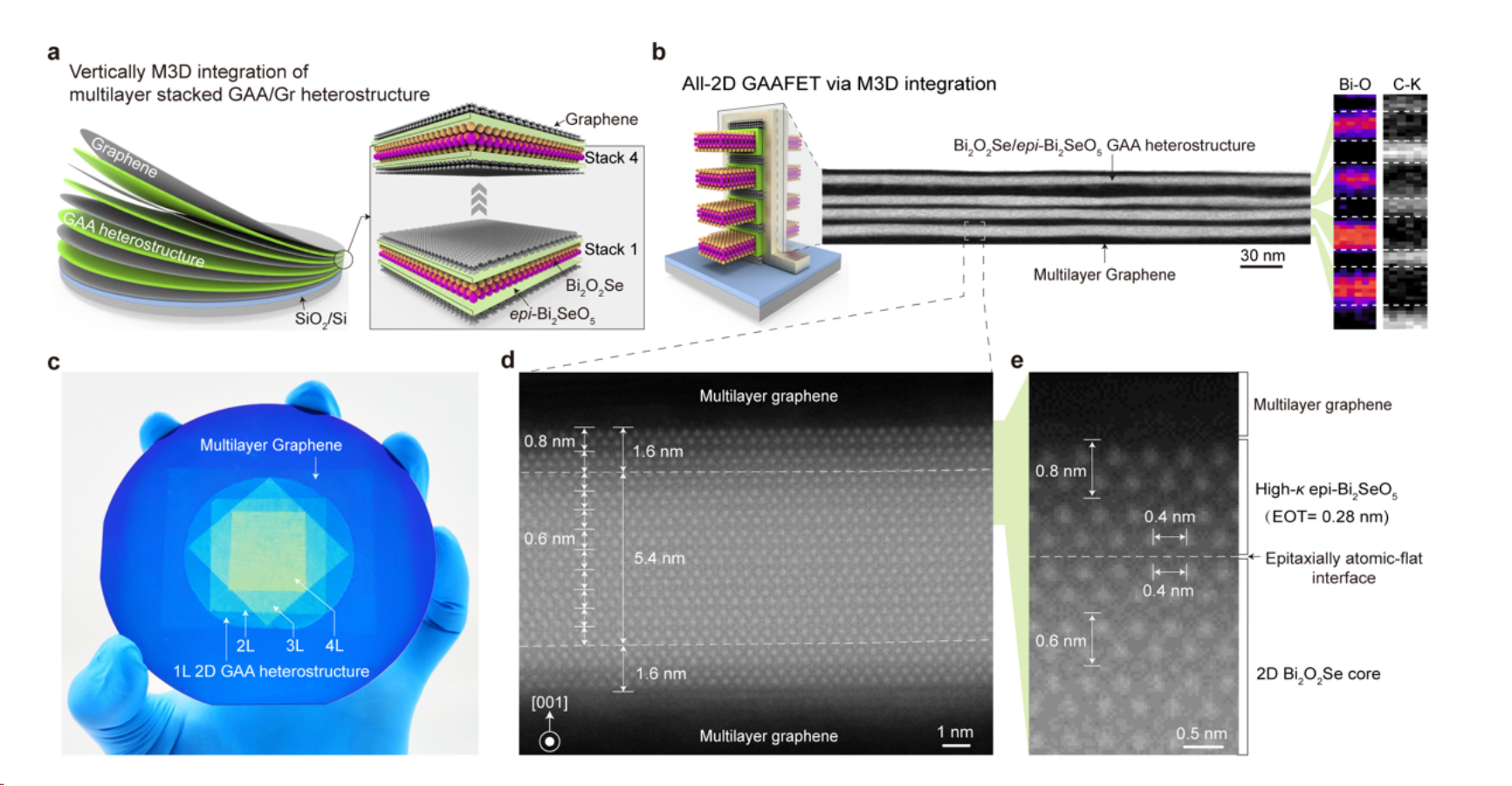

近期,该研究团队致力于将高迁移率二维铋基半导体与全环绕高κ超薄栅介质精准集成并极限微缩成三维新架构——二维环栅晶体管。他们基于独创的二维铋基半导体可控插层氧化方法,设计并制备了高质量的二维铋基半导体/环栅外延异质结,研制的二维环栅晶体管具有很高的界面质量和栅控能力,表现出高的迁移率(> 280 cm2/Vs)、低界面缺陷密度(~2×1011 cm-2 eV−1)、高电流开关比(108)和近热力学极限亚阈值摆幅(<62 mV/dec)等性能,满足业界高性能低功耗器件要求。进而,研究团队结合先进微纳加工技术和界面调控手段,成功构筑具有30 nm栅长的短沟道二维环栅晶体管。该二维铋基环栅晶体管具有原子级平整界面和超薄的0.27纳米等效氧化物厚度(EOT),在0.5 V的超低工作电压(VDD)下展现超高开态电流密度(> 1 mA/μm)、低本征延迟(Delay, 1.9 ps)及低能量延迟积(EDP,1.84 × 10−27 Js/μm)。在相同工作条件下,二维铋基环栅晶体管的性能超越英特尔(Intel)、台积电(TSMC)、比利时微电子中心(IMEC)报道的最先进环栅晶体管;其运算速度和能效同时超越当前商用硅基晶体管的最佳水平。研究团队报道的二维环栅晶体管满足国际器件和系统路线图(IRDS)对埃米节点的算力与功耗要求,是迄今为止速度最快、功耗最低的晶体管。

图3. 二维铋基环栅晶体管的电学特性。(a-c)二维铋基环栅晶体管的示意图(a),截面透射表征(b)和元素分析(c);(d,e)二维铋基环栅晶体管的转移特性曲线与可靠性;(f)与其它二维晶体管对比。

图4. 二维铋基环栅晶体管的电学性质。二维铋基环栅异晶体管的示意图(a),扫描电镜图(b,c),截面透射电镜图(d)和元素分析(e);晶体管的输出(f)和转移(g)特性及性能(h, i)与能效(j)的客观对标。

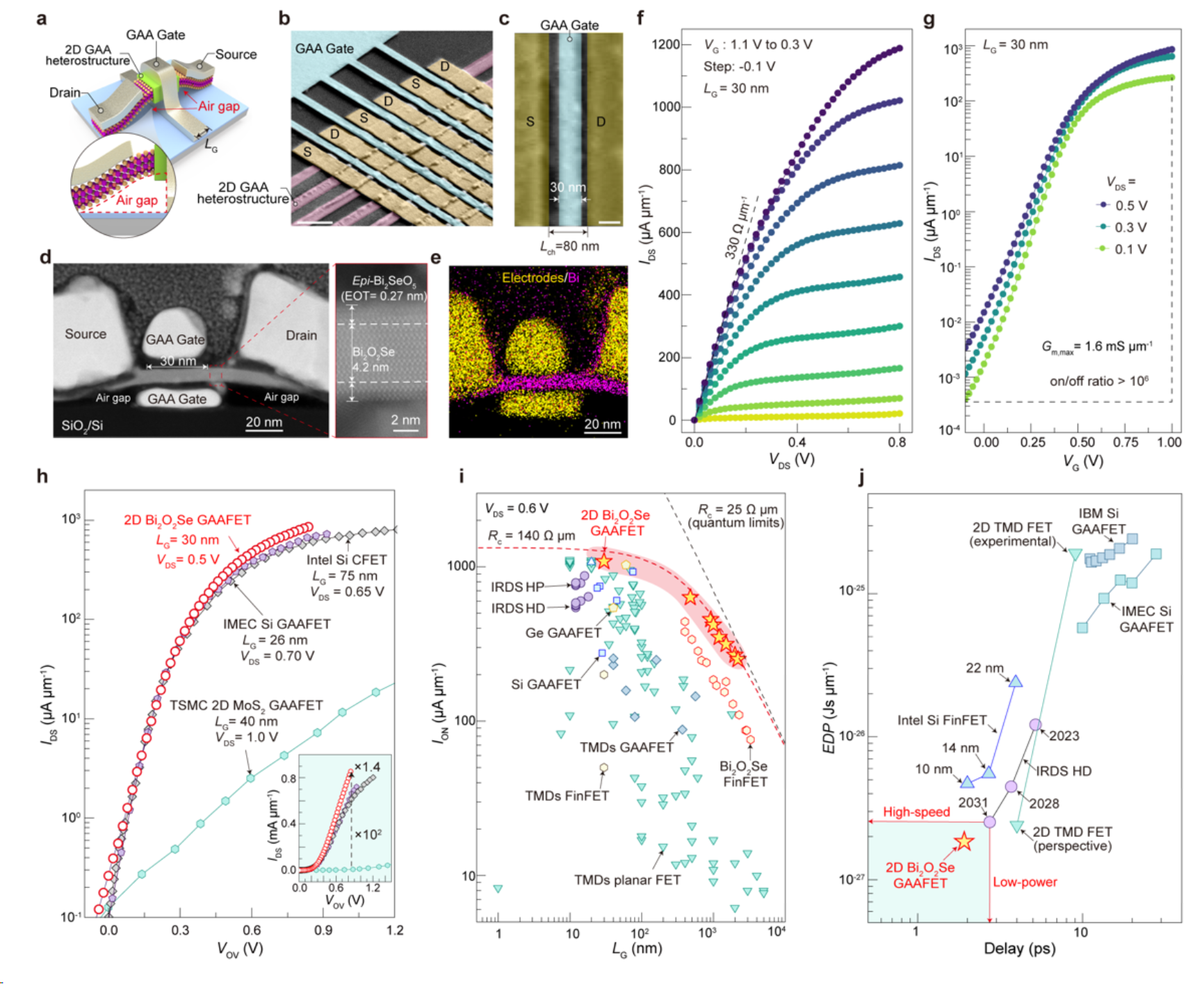

研究团队还基于上述环栅晶体管构筑了非门(NOT)、与非门(NAND)和或非门(NOR)等一系列逻辑单元器件,均可在超低功耗下实现其逻辑功能。其中非门可在超低工作电压(1.0 V)下展现出超高增益(59 V V-1)。

图5. 二维铋基环栅逻辑单元。二维铋基环栅非门示意图(a),工作曲线(b, c)、功耗(d, e)及增益对比(f); 二维铋基环栅或非门(g, h),与非门(i, j)的结构表征与功能。

综上所述,该项研究在国际上首次实现了高迁移率二维半导体/全环绕高κ氧化物外延异质结的精准合成与单片三维集成,并面向亚3纳米节点研制了低功耗、高性能二维环栅晶体管(2D GAAFET)及逻辑单元。该原创性工作突破了阻碍二维电子学发展的关键科学瓶颈,首次验证了二维环栅器件的性能和能耗上优于先进硅基技术,突破了后摩尔时代高速低功耗芯片的二维新材料精准合成与新架构三维异质集成瓶颈,为开发未来高性能芯片技术提供了全新的思路。

该研究成果以“Low-power 2D gate-all-around logics via epitaxial monolithic 3D integration”为题,近日发表于《自然-材料》(Nature Materials)。77779193永利集团彭海琳教授、电子学院邱晨光研究员、77779193永利集团谭聪伟副研究员为该论文的共同通讯作者;77779193永利集团博士研究生唐浚川、电子学院博士生姜建峰(现为麻省理工学院博士后)、77779193永利集团博士研究生高啸寅和博雅博士后高欣为文章的共同第一作者。该工作的其他主要合作者还包括深圳理工大学丁峰教授、永利集团电子学院彭练矛教授等。

图6. 彭海琳(右一)与课题组成员合影。

该研究得到了国家自然科学基金委、科技部、北京分子科学国家研究中心、新基石基金会科学探索奖、永利集团博雅博士后等资助,并得到了77779193永利集团分子材料与纳米加工实验室(MMNL)仪器平台的大力支持。

原文链接:https://doi.org/10.1038/s41563-025-02117-w

排版:高杨

审核:牛林,刘志博